芯片设计模板是预先设计好的电路模块,它们可以被设计师重用和定制,以加速芯片设计的过程。设计模板可以包括常见的电路结构、接口、内存控制器等。使用设计模板可以减少设计时间和成本,提高设计的一致性和可重用性。随着芯片设计的复杂性增加,设计模板的使用变得越来越普遍。然而,设计模板的选择和定制需要考虑目标应用的具体要求,以确保终设计的性能和可靠性。设计模板的策略性使用可以提升设计效率,同时保持设计的创新性和灵活性。AI芯片是智能科技的新引擎,针对机器学习算法优化设计,大幅提升人工智能应用的运行效率。四川DRAM芯片时钟架构

芯片设计是一项且复杂的工程,它要求设计师在宏观和微观层面上都具备全局视角。在宏观层面,设计师必须洞察市场趋势,了解消费者需求,同时确保产品功能与现有技术生态的兼容性。这涉及到对市场进行深入分析,预测未来技术发展,并与产品管理团队紧密合作,以确保设计满足目标市场的需求。在微观层面,设计师则需要专注于晶体管的精确布局、电路设计的优化以及信号路径的精确规划,这些细节对芯片的性能有着直接的影响。成功的芯片设计必须在宏观与微观之间找到恰当的平衡点,这不要求设计师具备深厚的技术知识,还需要他们对市场动态有敏锐的洞察力和预测能力。安徽芯片芯片前端设计阶段的高层次综合,将高级语言转化为具体电路结构。

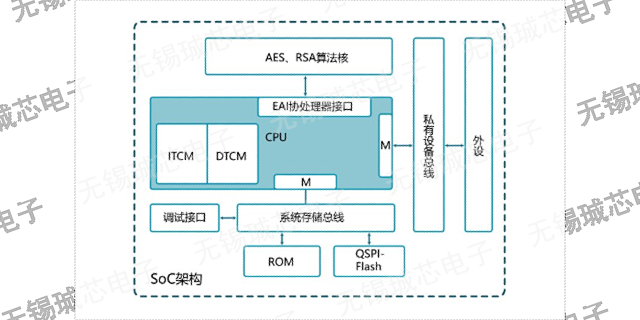

芯片国密算法的硬件实现是一个充满挑战的过程。设计师们需要将复杂的算法转化为可以在芯片上高效运行的硬件电路。这不要求算法本身的高效性,还要求电路设计满足低功耗和高可靠性的要求。此外,硬件实现还需要考虑到算法的可扩展性和灵活性,以适应不断变化的安全需求。设计师们需要通过优化算法和电路设计,以及采用高效的加密模式,来小化对芯片性能的影响。同时,还需要考虑到算法的更新和升级,以适应新的安全威胁。这要求设计师具备跨学科的知识和技能,以及对安全技术的深入理解。通过精心的设计和优化,芯片国密算法可以实现在不放弃性能的前提下,提供强大的安全保护。

芯片数字模块的物理布局是确保芯片整体性能达到预期目标的决定性步骤。布局的好坏直接影响到信号的传输效率,包括传输速度和信号的完整性。信号在芯片内部的传播延迟和干扰会降低系统的性能,甚至导致数据错误。此外,布局还涉及到芯片的热管理,合理的布局可以有效提高散热效率,防止因局部过热而影响芯片的稳定性和寿命。设计师们必须综合考虑信号路径、元件间的距离、电源和地线的布局等因素,精心规划每个模块的位置,以实现优的设计。这要求设计师具备深厚的专业知识和丰富的实践经验,以确保设计能够在满足性能要求的同时,也能保持良好的散热性能和可靠性。芯片设计模板内置多种预配置模块,可按需选择,以实现快速灵活的产品定制。

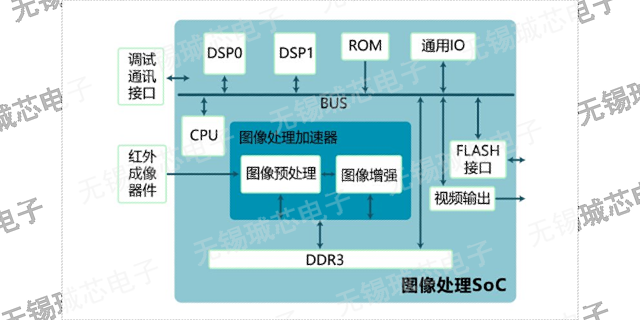

芯片架构是芯片设计中的功能,它决定了芯片的性能、功能和效率。架构设计师需要考虑指令集、处理单元、缓存结构、内存层次和I/O接口等多个方面。随着技术的发展,芯片架构正变得越来越复杂,新的架构如多核处理器、异构计算和可重构硬件等正在被探索和应用。芯片架构的创新对于提高计算效率、降低能耗和推动新应用的发展具有重要意义。架构设计师们正面临着如何在有限的硅片面积上实现更高计算能力、更低功耗和更好成本效益的挑战。数字模块物理布局的合理性,直接影响芯片能否成功应对高温、高密度封装挑战。上海ic芯片

芯片前端设计中的逻辑综合阶段,将抽象描述转换为门级网表。四川DRAM芯片时钟架构

芯片前端设计是将抽象的算法和逻辑概念转化为具体电路图的过程,这一步骤是整个芯片设计流程中的创新功能。前端设计师需要具备扎实的电子工程知识基础,同时应具备强大的逻辑思维和创新能力。他们使用硬件描述语言(HDL),如Verilog或VHDL,来编写代码,这些代码详细描述了电路的行为和功能。前端设计包括逻辑综合、测试和验证等多个步骤,每一步都对终产品的性能、面积和功耗有着决定性的影响。前端设计的成果是一张详细的电路图,它将成为后端设计的基础,因此前端设计的成功对整个芯片的性能和可靠性至关重要。四川DRAM芯片时钟架构